第一章 单元测试

1、判断题:

Verilog HDL的抽象分层建模方式可划分为系统级和算法级建模方式、寄存器级建模方式、逻辑门级建模方式和晶体管开关级建模方式。 ( )

选项:

A:错

B:对

答案: 【对】

2、判断题:

Verilog HDL是唯一一种硬件描述语言。( )

选项:

A:对

B:错

答案: 【错】

3、多选题:

以下哪些属于可编程逻辑器件( )

选项:

A:CPLD

B:PAL

C:GAL

D:FPGA

答案: 【CPLD

;PAL

;GAL

;FPGA

】

4、多选题:

以下哪些是FPGA和CPLD的相似点( )

选项:

A:可编程逻辑器件

B:采用SRAM工艺

C:可采用Verilog HDL 进行电路设计

D:器件密度可达到上千万门

答案: 【可编程逻辑器件

;可采用Verilog HDL 进行电路设计

】

5、多选题:

以下哪些是SOPC的基本特征( )

选项:

A:至少包含一个嵌入式处理器内核

B:可能包含部分模拟电路

C:低功耗

D:单芯片

答案: 【至少包含一个嵌入式处理器内核

;可能包含部分模拟电路

;低功耗

;单芯片

】

第二章 单元测试

1、单选题:

如果线网类型变量说明后未赋值,起始缺省值是( )

选项:

A:1

B:z

C:x

D:0

答案: 【z

】

2、单选题:

reg[7:0] mema[255:0]正确的赋值是 ( )

选项:

A:4’bxx11

B:4’bzz11

C:8’d0;

D:mema[5]=3’d0,

答案: 【mema[5]=3’d0,

】

3、单选题:

“a=4`b11001,b=4’bx110”选择正确的运算结果( )

选项:

A:a&b=0

B:b&a=x

C:b&&a=x

D:a&&b=1;

答案: 【a&&b=1;

】

4、单选题:

下列标识符中,( )是合法的标识符。

选项:

A:$finish

B:_date

C:8_sum

D:adder8#

答案: 【_date

】

5、单选题:

下列语句中,不属于并行语句的是( )。

选项:

A:元件例化语句

B:case语句

C:assign语句

D:过程语句

答案: 【case语句

】

第三章 单元测试

1、判断题:

阻塞性赋值符号为<=,非阻塞性赋值符号为=。( )

选项:

A:对

B:错

答案: 【】

2、判断题:

某一纯组合电路输入为in1,in2和in3,输出为out,则该电路描述中always的事件表达式应写为always@( in1,in2,in3 ); ( )

选项:

A:错

B:对

答案: 【】

3、判断题:

若某一时序电路由时钟clk信号上升沿触发,同步高电平复位信号rst清零,该电路描述中always的事件表达是应该写为always@( posedge clk or rst)。 ( )

选项:

A:错

B:对

答案: 【】

4、判断题:

Verilog HDL中内置了12种类型的基本门级元件模型。( )

选项:

A:错

B:对

答案: 【】

5、判断题:

bufif0是Verilog HDL中内置的基本门级元件:控制信号高电平有效的三态缓冲器。( )

选项:

A:对

B:错

答案: 【】

第四章 单元测试

1、判断题:

状态机常用状态编码有顺序编码、格雷码和独热码三种。 ( )

选项:

A:错

B:对

答案: 【】

2、判断题:

电路输出与电路输入有关的有限状态机电路被称为moore机。 ( )

选项:

A:对

B:错

答案: 【】

3、判断题:

采用有限状态机设计,易于构成性能良好的同步时序逻辑,有利于消除大规模逻辑电路中常见的竞争冒险现象。 ( )

选项:

A:对

B:错

答案: 【】

4、判断题:

有限状态机的代码可采用一段式、二段式和三段式描述方法。 ( )

选项:

A:对

B:错

答案: 【】

5、判断题:

有限状态机的三段式描述指包含三个always模块。 ( )

选项:

A:错

B:对

答案: 【】

第五章 单元测试

1、判断题:

评价Verilog代码的优劣不在于代码段的整洁简短,而在于代码是否能由综合工具流畅合理地转换成速度快和面积小的硬件形式。 ( )

选项:

A:对

B:错

答案: 【】

2、判断题:

异步设计非常容易产生毛刺现象和亚稳态。 ( )

选项:

A:对

B:错

答案: 【】

3、判断题:

使用双斜杠进行的注释行以分号结束;使用/* */进行的注释,/*和*/各占用一行,并且顶头。 ( )

选项:

A:对

B:错

答案: 【】

4、判断题:

相同功能的电路采用的代码风格不同,最终综合后的RTL电路结构依然是相同的。 ( )

选项:

A:对

B:错

答案: 【】

5、单选题:

以下信号名中,最具可读性的是( )

选项:

A:addr_count

B:add1

C:addr_1

D:addr11

答案: 【

】

第六章 单元测试

1、多选题:

Testbench的主要功能是( )

选项:

A:为设计电路提供激励信号;

B:复杂设计可以使用EDA工具,或者通过用户接口自动比较仿真结果与理想值,实现结果的自动检查。

C:正确例化设计电路;

D:将仿真数据显示在终端或存为文件,也可以显示在波形窗口中以供分析检查;

答案: 【

】

2、多选题:

以下哪些系统任务实现文本输出( )

选项:

A:$write;

B:$display;

C:$monitor。

D:$strobe;

答案: 【$write;

;$display;

;$monitor。

;$strobe;

】

3、多选题:

以下哪些系统函数实现读取当前仿真时间( )

选项:

A:$stime;

B:$ time;

C:$realtime;

D:$htime。

答案: 【

】

4、判断题:

系统函数和任务一般以符号#开头。 ( )

选项:

A:错

B:对

答案: 【】

5、判断题:

$write与$display相同,不同的是不会自动换行. ( )

选项:

A:错

B:对

答案: 【】

第七章 单元测试

1、判断题:

Altera公司的Quartus II和公司的ModelSim是两种目前世界上比较流行和实用的EDA工具软件。 ( )

选项:

A:错

B:对

答案: 【】

2、判断题:

Quartus II可以采用文本输入法和图形输入法进行电路设计。 ( )

选项:

A:对

B:错

答案: 【】

3、判断题:

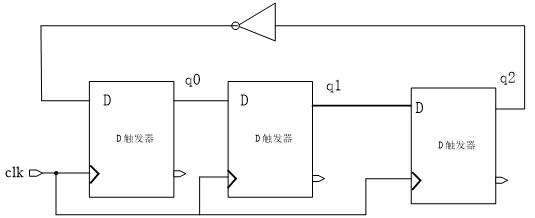

根据下面的程序,

always@(posedge clk)

begin

q0<=~q2;

q1<=q0;

q2<=q1;

end画出综合出来的电路图如图所示。 ( )

( )

选项:

A:错

B:对

答案: 【】

4、判断题:

分析下列程序,得到10时刻执行结果a=1,15时刻b=1,20时刻c=1。

initial

fork

#10 a = 1;

#15 b = 1;

begin

#20 c = 1

#10 d = 1;

end

#25 e = 1;

Join

( )

选项:

A:对

B:错

答案: 【】

5、单选题:

选择下面两段代码正确的一个。 ( )

选项:

A:

module example(o1, o2, a, b, c, d);

input a, b, c, d;

output o1, o2;

reg o1;

and u1(o2, c, d);

always @(a or b)

if (a) o1 = b; else o1 = 0;

endmodule

B:

module example(o1, o2, a, b, c, d);

input a, b, c, d;

output o1, o2;

reg c, d, o2;

and u1(o2, c, d);

always @(a or b)

if (a) o1 = b; else o1 = 0;

endmodule

答案: 【

】

请先 !