第一章 单元测试

1、单选题:

一位十六进制数可以用( )位二进制数来表示。

选项:

A:1

B:2

C:4

D:3

答案: 【4】

2、单选题:

十进制数43可转换为( )8421BCD码。

选项:

A: 10011

B: 1000011

C: 010011

D: 01000011

答案: 【 01000011】

3、单选题:

二进制数+1011的反码为( )。

选项:

A: 00100

B: 01011

C: 11011

D: 10100

答案: 【 01011】

4、单选题:

有符号二进制数-89的补码为( )。

选项:

A: 10100111

B: 00100111

C: 01011001

D: 11011001

答案: 【 10100111】

5、多选题:

与模拟电路相比,数字电路主要的优点有( )。

选项:

A: 抗干扰能力强

B: 保密性好

C: 通用性强

D: 容易设计

答案: 【 抗干扰能力强; 保密性好; 通用性强】

6、多选题:

与八进制数(47.3)8等值的数为( )。

选项:

A:(27.6)16

B:(100111.011)2

C: (27.3 )16

D: (100111.11)2

答案: 【(27.6)16;(100111.011)2】

7、多选题:

以下代码中为恒权码的为( )。

选项:

A: 8421BCD码

B: 格雷码

C: 余三码

D: 5421BCD码

答案: 【 8421BCD码; 5421BCD码】

8、多选题:

与十进制数(53.5)10等值的数或代码为( )。

选项:

A: (0101 0011.0101)8421BCD

B: (65.4)8

C: (110101.1)2

D: (35.8)16

答案: 【 (0101 0011.0101)8421BCD; (65.4)8; (110101.1)2; (35.8)16】

9、多选题:

在一个8位的存储单元中,能够存储的最大无符号整数是( )。

选项:

A:(256)10

B:(255)10

C:(FF)16

D:(127)10

答案: 【(255)10;(FF)16】

10、多选题:

矩形脉冲信号的参数有( )。

选项:

A: 脉宽

B: 占空比

C: 周期

D: 扫描期

答案: 【 脉宽; 占空比; 周期】

11、多选题:

常用的BCD码有( )。

选项:

A: 格雷码

B: 余三码

C: 8421码

D: 奇偶校验码

答案: 【 余三码; 8421码】

12、多选题:

以下几种编码中,可靠性编码是( )。

选项:

A: 5421码

B: 奇偶校验码

C: 8421码

D: 格雷码

答案: 【 奇偶校验码; 格雷码】

第二章 单元测试

1、单选题:

利用约束项化简逻辑函数时,约束项应看成( )。

选项:

A: 能使圈组大的看成1,其它看成0

B:2

C: 无所谓

D:1

答案: 【 能使圈组大的看成1,其它看成0】

2、单选题:

下面的卡诺图化简,应画( )个包围圈。

选项:

A: 5

B: 3

C: 4

D: 2

答案: 【 4】

3、单选题:

已知两输入逻辑变量AB和输出结果Y的真值表如下表,则AB的逻辑关系为( )。

| A | B | Y |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

选项:

A: 异或

B: 或非

C: 与非

D: 同或

答案: 【 异或】

4、单选题:

利用卡诺图化简逻辑函数时,8个相邻的最小项可消去( )个变量。

选项:

A: 2

B: 3

C: 1

D: 4

答案: 【 3】

5、单选题:

在函数L(A,B,C,D)=AB+CD的真值表中,L=1的状态有( )。

选项:

A: 2

B: 7

C: 4

D: 6

答案: 【 7】

6、单选题:

在同一逻辑函数式中,下标号相同的最小项和最大项是( )关系。

选项:

A: 相等

B: 没有关系

C: 互补

D: 相加等于1

答案: 【 互补】

7、单选题:

F=ABCD’+ABD+BCD’+ABC+BD+BC’ 化简为最简与或式( )。

选项:

A: B

B: A’+B’+C’+D

C: ACD

D:ACD+BCD

答案: 【 B】

8、多选题:

逻辑变量的取值1和0可以表示( )。

选项:

A: 真与假

B: 电流的有、无

C: 电位的高、低

D: 开关的闭合、断开

答案: 【 真与假; 电流的有、无; 电位的高、低; 开关的闭合、断开】

9、多选题:

逻辑函数的表示方法中具有唯一性的是( )。

选项:

A: 逻辑图

B: 表达式

C: 卡诺图

D: 真值表

答案: 【 卡诺图; 真值表】

10、多选题:

F=AB’+BD+CDE+A’D=

选项:

A: (A+D)(B+D’)

B: AB’+D

C:(A+B’)D

D: (A+D)(B’+D)

答案: 【 AB’+D; (A+D)(B’+D)】

11、多选题:

求一个逻辑函数F的对偶式,可将F中的( )。

选项:

A: 原变量换成反变量,反变量换成原变量

B:常数中“0”换成“1”,“1”换成“0”

C:“·”换成“+”,“+”换成“·”

D:变量不变

答案: 【常数中“0”换成“1”,“1”换成“0” ;“·”换成“+”,“+”换成“·” ;变量不变 】

12、多选题:

在何种输入情况下( ),“或非”运算的结果是逻辑0。

选项:

A:任一输入为1

B:任一输入为0,其他输入为1

C:全部输入是0

D:全部输入是1

答案: 【任一输入为1 ;任一输入为0,其他输入为1 ;全部输入是1 】

13、判断题:

8421BCD码是二–十进制码。

选项:

A:对

B:错

答案: 【对】

14、判断题:

与逻辑是至少一个条件具备事件就发生的逻辑。

选项:

A:错

B:对

答案: 【错】

15、判断题:

L等于A和B的异或,其表达式是L=A+B

选项:

A:错

B:对

答案: 【错】

16、判断题:

“同或”逻辑功能是两个输入变量A、B相同时,输出为1;A、B不同时,输出为0。

选项:

A:错

B:对

答案: 【对】

17、判断题:

已知逻辑函数A+B=A+C,AB=AC,则B=C

选项:

A:对

B:错

答案: 【对】

18、判断题:

对逻辑函数Y=A + B+ C+B 利用代入规则,令A=BC代入,得Y= BC + B+ C+B = C+B 成立。

选项:

A:错

B:对

答案: 【错】

第三章 单元测试

1、单选题:

逻辑表达式Y=AB可以用( )直接实现。

选项:

A:非门

B:与门

C:或门

答案:

2、单选题:

OC门在使用时须在( )之间接一电阻。

选项:

A:输出与输入

B:输出与电源

C:输出与地

答案:

3、单选题:

能实现总线连接方式的门为( )。

选项:

A:TTL或非门

B:TTL与非门

C:OC门

D:TTL三态门

答案:

4、单选题:

CMOS逻辑电路是以( )为基础的集成电路。

选项:

A:NMOS管和PMOS管

B:三极管

C:NMOS管

D:PMOS管

答案:

5、单选题:

TTL电路是( )的集成电路。

选项:

A:以场效应管为基础

B:以晶体三极管为基础

C:以二极管为基础

D:以晶闸管为基础

答案:

6、多选题:

对于TTL与非门,其闲置输入端的处理,可以( )。

选项:

A:接地

B:与有用输入端并联

C:通过电阻3kΩ接电源

D:接电源

答案:

7、多选题:

以下电路中可以实现“线与”功能的有( )。

选项:

A:集电极开路门

B:与非门

C:三态输出门

D:漏极开路门

答案:

8、多选题:

三极管作为开关使用时,要提高开关速度,可( )。

选项:

A:增加饱和深度

B:采用有源泄放回路

C:采用抗饱和三极管

D:降低饱和深度

答案:

9、多选题:

CMOS数字集成电路与TTL数字集成电路相比突出的优点是( )。

选项:

A:高速度

B:微功耗

C:高抗干扰能力

D:电源范围宽

答案:

10、判断题:

基本型的TTL门电路输出端不允许相互并联,否则将损坏器件。

选项:

A:对

B:错

答案:

11、判断题:

或非门的多余输入端不能接高电平。

选项:

A:错

B:对

答案:

12、判断题:

一般TTL门电路的输出端可以直接相连,实现线与。

选项:

A:错

B:对

答案:

13、判断题:

CMOS “OD门” 的输出端可连接在一起实现“线与”。

选项:

A:错

B:对

答案:

14、判断题:

对于TTL与非门,只要有一个输入为低电平,输出即为高电平,所以对与非门多余输入端的处理不能接低电平。

选项:

A:对

B:错

答案:

15、判断题:

普通的逻辑门电路的输出端不可以并联在一起,否则可能会损坏器件。

选项:

A:错

B:对

答案:

16、判断题:

CMOS 电路比 TTL 电路功耗大。

选项:

A:错

B:对

答案:

17、判断题:

TTL与非门输入端接+5V时,逻辑上属于输入“1”。

选项:

A:对

B:错

答案:

18、判断题:

CMOS门电路可以把输出端并联使用以实现“线与”逻辑。

选项:

A:错

B:对

答案:

19、判断题:

CMOS或非门与TTL或非门的逻辑功能完全相同。

选项:

A:错

B:对

答案:

第四章 单元测试

1、单选题:

一个译码器若有100个译码输出端,则译码输入端有( )个。

选项:

A:5

B:7

C:6

D:8

答案:

2、单选题:

当编码器 74HC148 的输入端 I1’ 、 I5’ 、 I6’ 、 I7’ 为低电平,其余输入端为高电平时,则输出的编码信号为( )。

选项:

A:001

B:111

C:000

D:110

答案:

3、单选题:

在下列选项中,不是组合电路的有( )。

选项:

A:数值比较器

B:计数器

C:编码器

D:译码器

答案:

4、单选题:

一个八选一的数据选择器,( )数据输入端。

选项:

A:有1个

B:有2个

C:有8个

D:有3个

答案:

5、多选题:

消除组合逻辑电路“竞争-冒险”的方法有( )。

选项:

A:引入选通脉冲

B:后级加缓冲电路

C:在输出端接入滤波电容

D:修改逻辑设计

答案:

6、判断题:

共阴接法发光二极管数码显示器需选用有效输出为高电平的七段显示译码器来驱动。

选项:

A:错

B:对

答案:

7、判断题:

优先编码器的编码信号是相互排斥的,不允许多个编码信号同时有效。

选项:

A:对

B:错

答案:

8、判断题:

用4选1数据选择器不能实现3变量的逻辑函数。

选项:

A:错

B:对

答案:

9、单选题:

选出与下面所示逻辑电路图对应的逻辑关系式为( )。

选项:

A:Y=ABC

B:![]()

C:Y=A+B+C

D:Y=AC+BD

答案:

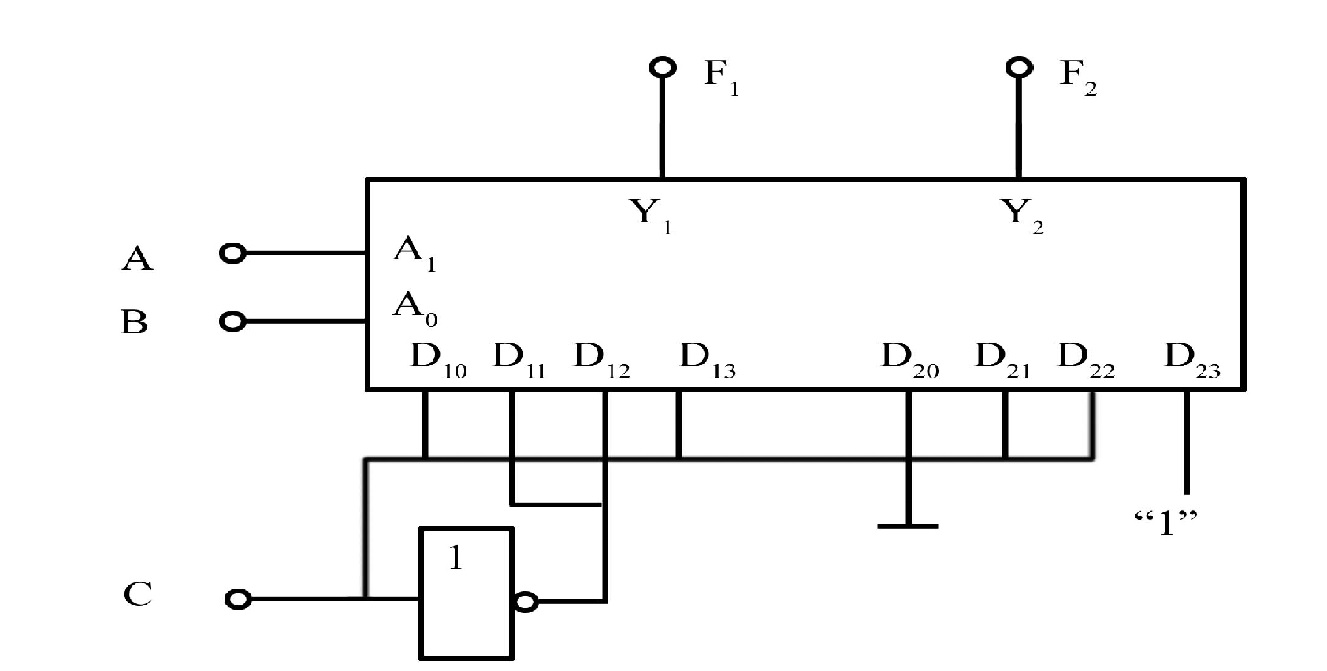

10、单选题:

双四选一数据选择器构成的组合逻辑电路,输入变量为A、B、C,输出逻辑函数为F1 、F2,其功能为( )。

选项:

A:F1 =∑m(1,2,4,7),F2=∑m(1,3,6,7),全减器

B:F1 =∑m(1,2,3,7),F2=∑m(3,5,6,7),全减器

C:F1 =∑m(1,2,4,7),F2=∑m(4,5,6,7), 全加器

D:F1 =∑m(1,2,4,7),F2=∑m(3,5,6,7), 全加器

答案:

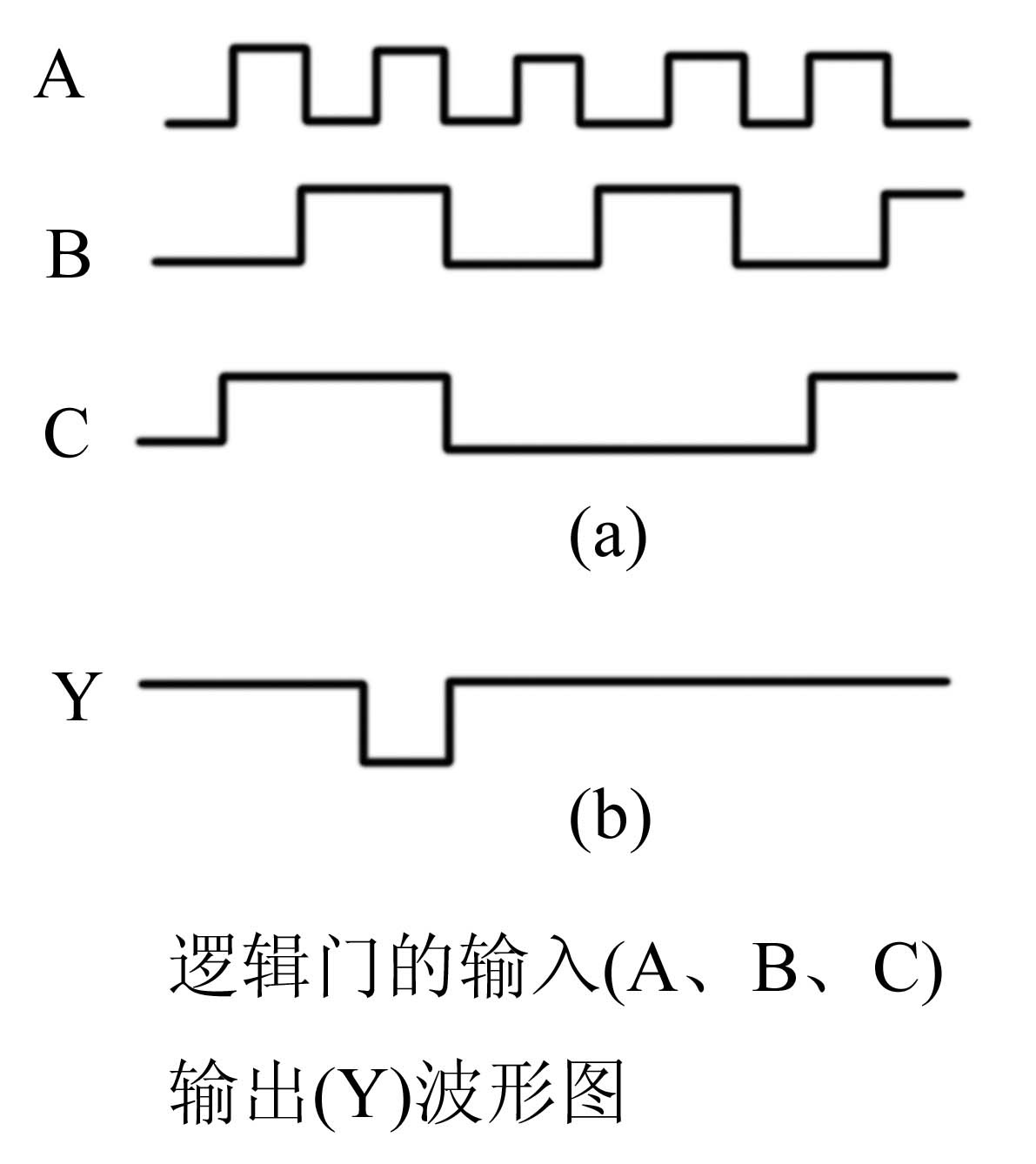

11、单选题:

已知有一个3输入端的门电路,若输入信号A、B、C的波形如图 (a)所示,输出信号Y的波形如图(b)所示,则该门电路执行的是( )逻辑操作。

选项:

A:与非

B:与

C:或非

D:或

答案:

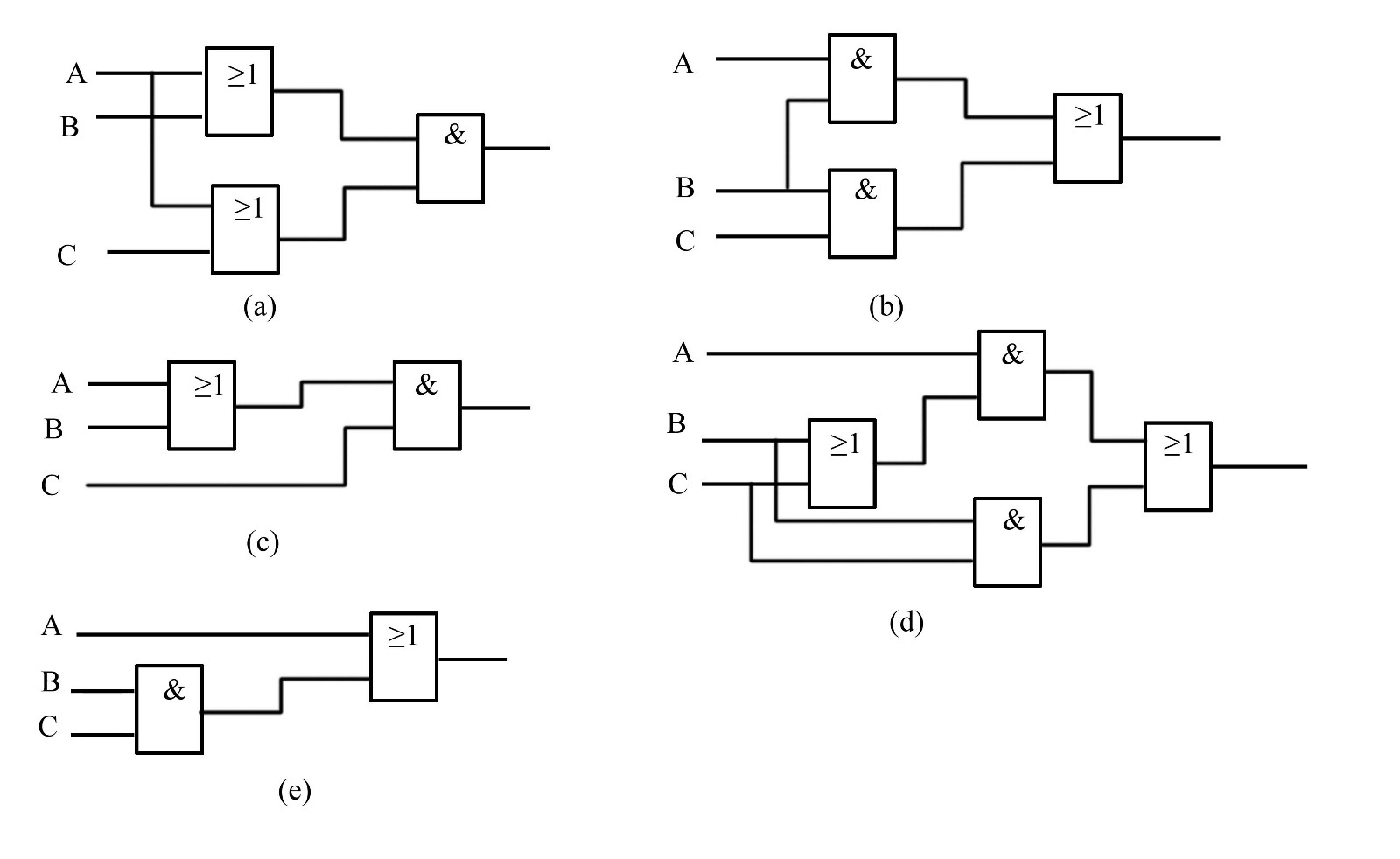

12、单选题:

在图中,选出与下列逻辑式顺序对应的逻辑图是( )。 Y1=(A+B)C Y2=AB+BC Y3=(A+B)(A+C) Y4= A+BC Y5=A(B+C)+BC

选项:

A:(b),(c),(a),(e),(d)

B:(a),(e),(d),(c),(b)

C:(c),(b),(a),(e),(d)

D:(c),(b),(d),(a),(e)

答案:

13、单选题:

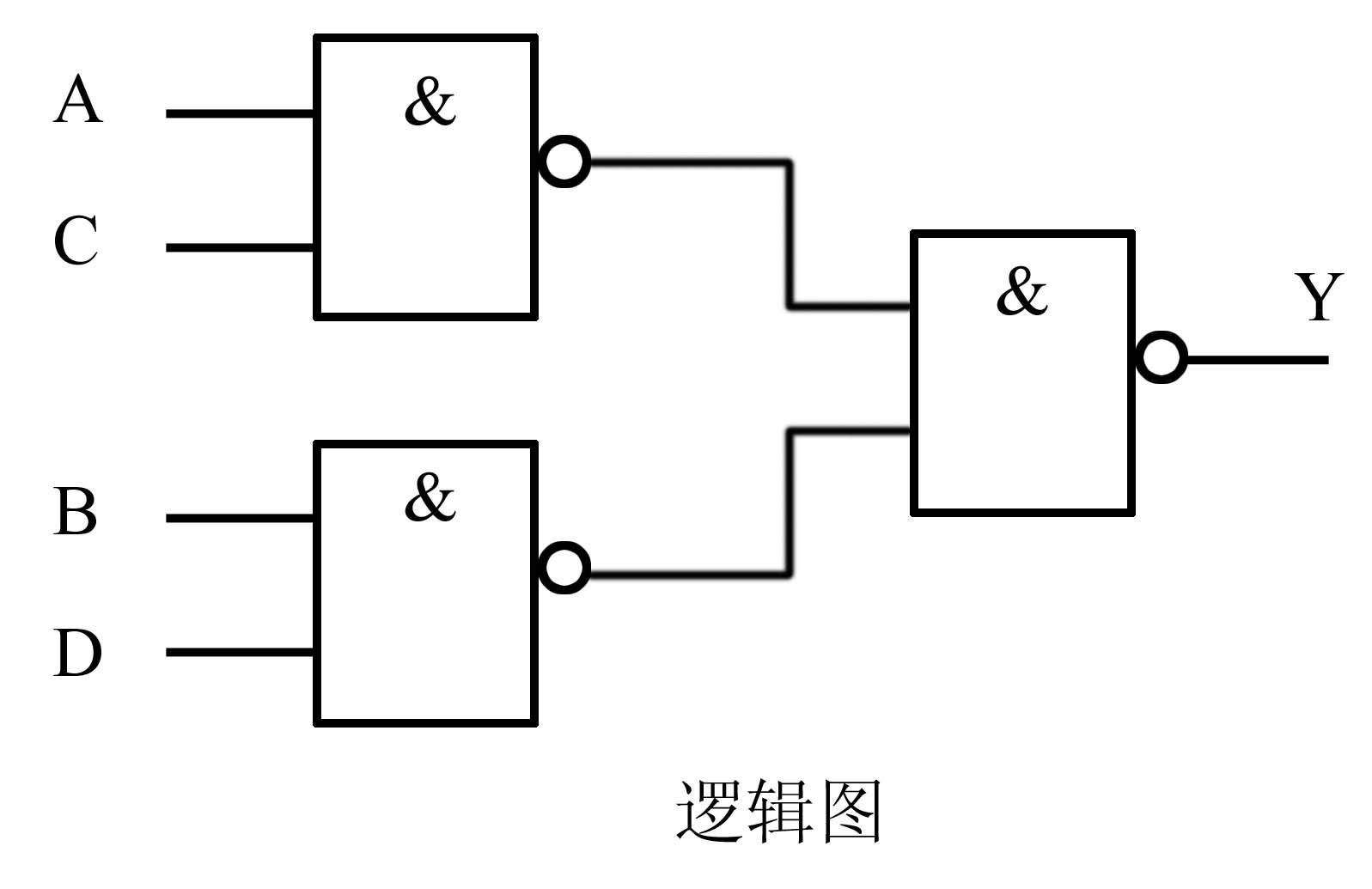

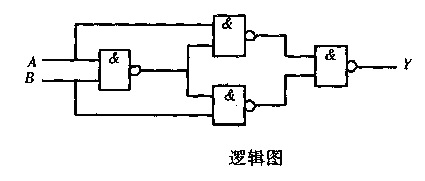

指出下图用“与非门”组成电路的逻辑关系是( )。

选项:

A:“或非”关系

B:“异或”关系

C:“与非”关系

D:“同或”关系

答案:

14、单选题:

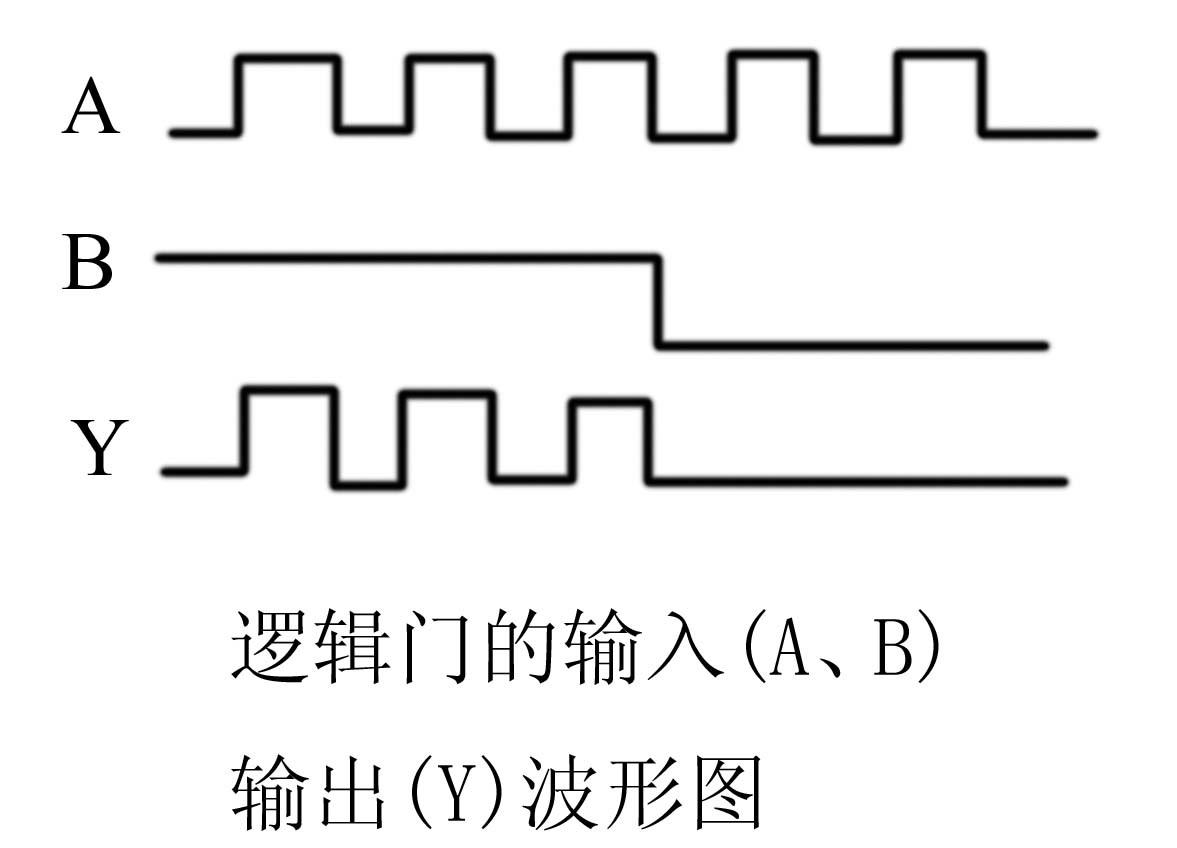

A、B为逻辑门的2个端入端,Y为输出。A、B和Y的波形如下图所示,则该门实现的是( )。

选项:

A:“或”逻辑功能

B:“与非”逻辑功能

C:“或非”逻辑功能

D:“与”逻辑功能

答案:

15、单选题:

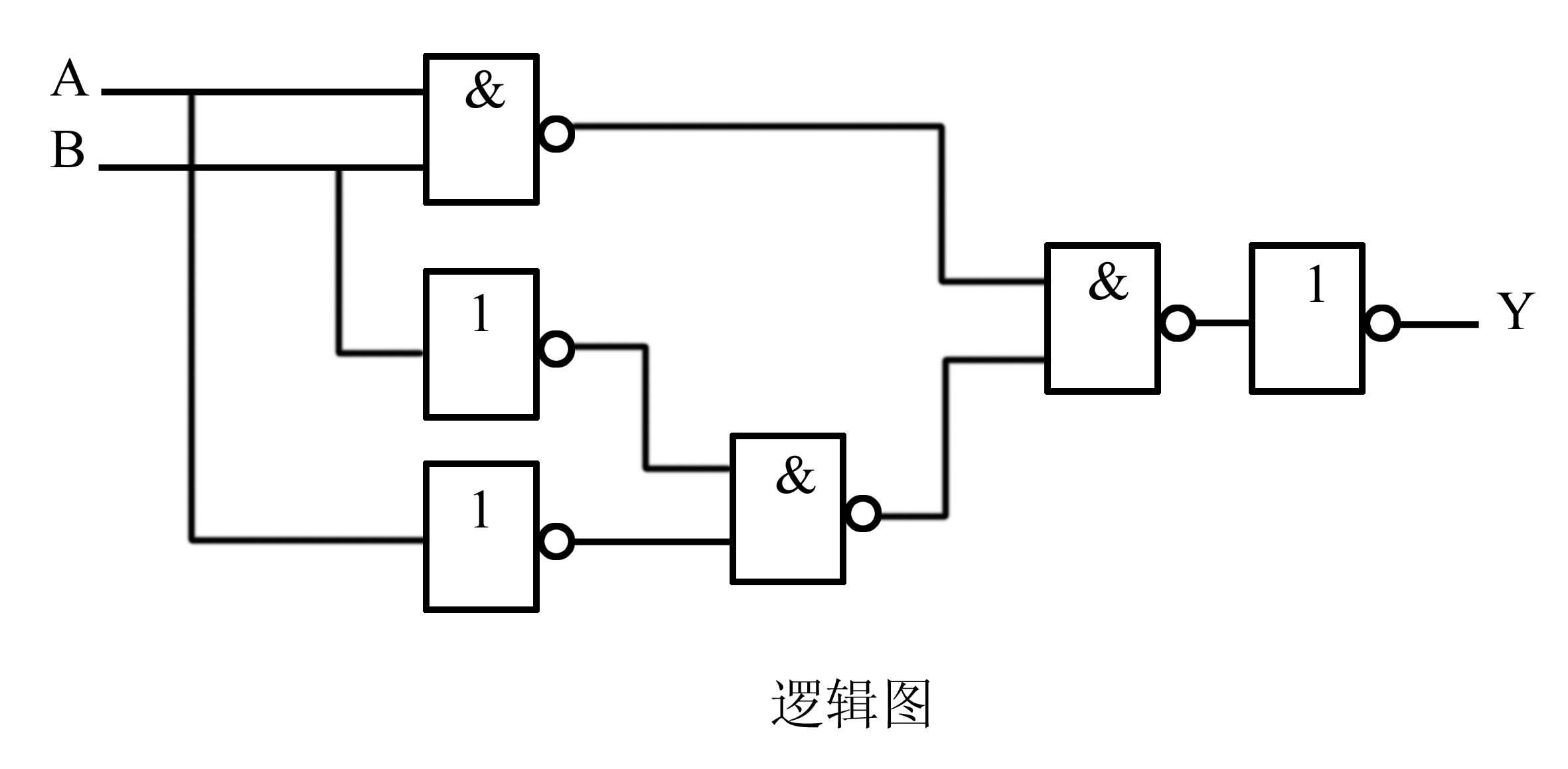

选出与下图对应的逻辑式( )。

选项:

A:![]()

B:![]()

C:![]()

D:![]()

答案:

16、单选题:

设计一个裁判表决电路。裁判组由三人组成,分别为:主裁判A,副裁判B和副裁判C。判定比赛的规则如下:只有当两个或两个以上裁判支持,并且其中有一个是主裁判时,比赛结果的裁决才有效。令A、B、C为1表示支持,为0表示反对。裁决结果Y为1表示有效,Y为0表示无效。下列表达式中能实现改电路功能的是( )。

选项:

A:Y=ABC

B:Y=A+BC

C:Y=A+B+c

D:Y=AB+AC

答案:

17、单选题:

组合逻辑电路中的竞争-冒险是由于( )引起的。

选项:

A:触发器的延时

B:最大项

C:门电路的传输延迟

D:最小项

答案:

18、判断题:

能实现两个1位二进数和来自低位的进位相加的电路叫全加器。

选项:

A:错

B:对

答案:

19、判断题:

串行进位加法器的缺点是运算速度慢,优点是电路结构简单。超前进位加法器的优点是运算速度快,缺点是电路结构复杂。

选项:

A:对

B:错

答案:

20、判断题:

组合逻辑电路由逻辑门和触发器构成。

选项:

A:错

B:对

答案:

第五章 单元测试

1、单选题:

触发器是一种( )。

选项:

A:单稳态电路

B:双稳态电路

C:无稳态电路

D:三稳态电路

答案:

2、单选题:

当与非门构成的基本SR锁存器处于置0状态时,其输入信号S、R取值应为( )。

选项:

A:1 0

B:0 1

C:1 1

D:0 0

答案:

3、单选题:

使触发器的状态变化分两步完成的触发方式是( )。

选项:

A:维持阻塞触发方式

B:脉冲触发方式

C:电平触发方式

D:边沿触发方式

答案:

4、单选题:

下列哪一种触发器容易产生“直通”问题?( )

选项:

A:主从JK触发器

B:边沿D触发器

C:同步SR触发器

D:主从SR触发器

答案:

5、单选题:

JK触发器处于翻转状态时,输入信号的条件是( )。

选项:

A:J=1,K=0

B:J=0,K=0

C:J=1,K=1

D:J=0,K=1

答案:

6、单选题:

对于D触发器,若CP脉冲到来前所加的激励信号D=1,可以使触发器的状态( )。

选项:

A:不变

B:置1

C:翻转

D:置0

答案:

7、单选题:

对于T触发器,当T=( )时,触发器处于保持状态。

选项:

A:0、1均可

B:其余选项都不正确

C:0

D:1

答案:

8、单选题:

某存储器具有8根地址线和8根双向数据线,则该存储器的容量为( )。

选项:

A:256×8

B:8×3

C:256×256

D:8K×8

答案:

9、单选题:

寻址容量为16K×8的RAM需要( )根地址线。

选项:

A:4

B:16

C:8

D:14

答案:

10、多选题:

能够存储二值信息的器件有( )。

选项:

A:触发器

B:只读存储器

C:随机存储器

D:寄存器

答案:

11、多选题:

JK触发器( )。

选项:

A:具有“翻转”功能

B:具有“置1”功能

C:具有“置0”功能

D:具有“保持”功能

答案:

12、多选题:

下列触发器中,没有约束条件的是( )。

选项:

A:T触发器

B:SR触发器

C:JK触发器

D:D触发器

答案:

13、多选题:

JK触发器初始状态Q=1,欲使JK触发器次态按Q*=1工作,可使JK触发器的输入端( )。

选项:

A:J=0,K=1

B:J=K=0

C:J=K=1

D:J=1,K=0

答案:

14、判断题:

触发器的输出包含两个暂稳态。

选项:

A:对

B:错

答案:

15、判断题:

主从JK触发器、边沿JK触发器和同步JK触发器的逻辑功能完全相同。( )

选项:

A:错

B:对

答案:

第六章 单元测试

1、单选题:

一般情况下,时序逻辑电路在结构上包含( )。

选项:

A:组合逻辑电路和存储电路

B:组合逻辑电路

C:触发器

D:存储电路

答案:

2、单选题:

Mealy型时序逻辑电路的输出是( )。

选项:

A:只与电路当前状态有关

B:与输入和电路当前状态均有关

C:与输入和电路当前状态均无关

D:只与输入有关

答案:

3、单选题:

一个4位串行数据输入的移位寄存器,时钟脉冲频率为1kHz,完成转换4位并行数据输出的时间为( )。

选项:

A:8µs

B:8ms

C:4µs

D:4ms

答案:

4、单选题:

要构成七进制计数器,( )。

选项:

A:至少需要2个触发器

B:至少需要7个触发器

C:至少需要5个触发器

D:至少需要3个触发器

答案:

5、单选题:

N个触发器可以构成最大计数长度(进制数)为( )的计数器。

选项:

A:2N

B:N-1

C:N+1

D:N

答案:

6、单选题:

一个5位的二进制加计数器,由00000状态开始,经过75个时钟脉冲后,此计数器的状态为( )。

选项:

A:01011

B:00111

C:01100

D:01010

答案:

7、单选题:

n位扭环形计数器中,无效状态的个数为( )。

选项:

A:2n-1

B:2n-2n

C:2n-n

D: 2n

答案:

8、单选题:

把一个五进制计数器与一个四进制计数器串联可得到( )进制计数器。

选项:

A:20

B:4

C:9

D:5

答案:

9、单选题:

4位移位寄存器,现态Q0Q1Q2Q3为1100,经左移1位后其次态为( )。

选项:

A:0011或1011

B:0011或1111

C:1011或1110

D:1000或1001

答案:

10、单选题:

欲设计0,1,2,3,4,5,6,7这几个数的计数器,如果设计合理,采用同步二进制计数器,最少应使用( )级触发器。

选项:

A:5

B:4

C:2

D:3

答案:

11、单选题:

五个D触发器构成环形计数器,其计数长度为( )。

选项:

A:5

B:10

C:32

D:25

答案:

12、多选题:

移位寄存器的逻辑功能包括( )。

选项:

A:移位

B:寄存数码

C:计数

D:数据转换

答案:

13、多选题:

下面几项属于时序逻辑电路的是( )。

选项:

A:序列脉冲发生器

B:数码寄存器

C:计数器

D:移位寄存器

答案:

14、多选题:

由两片74LS161芯片构成29进制加法计数器,两片计数器芯片的连接方式有( )。

选项:

A:反馈

B:串行进位

C:并行进位

D:同步预置数

答案:

15、判断题:

同步二进制计数器的电路比异步二进制计数器复杂,所以实际应用中较少使用同步二进制计数器。

选项:

A:对

B:错

答案:

16、判断题:

环形计数器如果不作自启动修改,则总有孤立状态存在。

选项:

A:对

B:错

答案:

17、判断题:

环形计数器在每个时钟脉冲CP作用时,仅有一位触发器发生状态更新。

选项:

A:对

B:错

答案:

第七章 单元测试

1、单选题:

只有暂稳态的电路是( )。

选项:

A:定时器

B:单稳态电路

C:多谐振荡器

D:施密特触发器

答案:

2、单选题:

单稳态触发器有( )。

选项:

A:计数功能

B:整形功能

C:定时和延时功能

D:定时、延时和整形功能

答案:

3、单选题:

一个由555定时器构成的单稳态触发器的正脉冲宽度为( )。

选项:

A:0.7RC

B:1.4RC

C:RC

D:1.1RC

答案:

4、单选题:

石英晶体多谐振荡器的最突的出优点是( )。

选项:

A:振荡频率稳定

B:电路简单

C:输出波形边沿陡峭

D:速度高

答案:

5、单选题:

用555定时器组成施密特触发器,当输入控制端CO外接10V电压时,回差电压为( )。

选项:

A:6.66V

B:10V

C:3.33V

D:5V

答案:

6、单选题:

以下各电路中,可以产生脉冲用于定时的是( )。

选项:

A:单稳态触发器

B:石英晶体多谐振荡器

C:多谐振荡器

D:施密特触发器

答案:

7、单选题:

555定时器的2脚、6脚接在一起构成( )。

选项:

A:多谐振荡器

B:基本RC触发器

C:施密特触发器

D:单稳态触发器

答案:

8、单选题:

555定时器的TH端、TR端的电平分别小于2VDD/3和VDD/3时定时器的输出状态是( )。

选项:

A:0

B:1

C:不确定

D:原状态

答案:

9、判断题:

单稳态触发器的暂稳态维持时间用tW表示,与电路中RC成正比。

选项:

A:对

B:错

答案:

10、判断题:

施密特触发器可用于将三角波变换成正弦波。

选项:

A:对

B:错

答案:

11、判断题:

施密特触发器的正向阈值电压VT+一定大于负向阈值电压VT-。

选项:

A:对

B:错

答案:

12、判断题:

单稳态触发器的暂稳态时间与输入触发脉冲宽度成正比。

选项:

A:对

B:错

答案:

13、判断题:

多谐振荡器的输出信号的周期与阻容元件的参数成正比。

选项:

A:对

B:错

答案:

14、多选题:

脉冲整形电路有( )。

选项:

A:施密特触发器

B:555定时器

C:多谐振荡器

D:单稳态触发器

答案:

第八章 单元测试

1、多选题:

D/A转换器产生转换误差的原因有( )。

选项:

A:运算放大器的零点漂移

B:模拟开关导通内阻和导通压降的差异

C:参考电压的波动

D:电阻网络中电阻阻值的偏差

答案:

2、多选题:

一个无符号10位数字输入的DAC,其输出电平的级数为( )。

选项:

A:10

B:1024

C:2的10次方

D:4

答案:

3、判断题:

在相同的基准电压下,D/A转换器的位数越多,能够分辨的最小输出电压变化量就越小。

选项:

A:对

B:错

答案:

4、判断题:

权电阻网络D/A转换器的电路简单且便于集成工艺制造,因此被广泛使用。

选项:

A:对

B:错

答案:

5、判断题:

D/A转换器的最大输出电压的绝对值可达到基准电压VREF。

选项:

A:错

B:对

答案:

6、判断题:

D/A转换器的位数越多,转换精度越高。

选项:

A:错

B:对

答案:

7、单选题:

为使采样输出信号不失真地代表输入模拟信号,采样频率fs和输入模拟信号的最高频率fim的关系是fs( )fim。

选项:

A:≤2

B:≤

C:≥

D:≥2

答案:

8、单选题:

在位数不同的D/A转换器中,分辨率最高的是( )。

选项:

A:10位

B:8位

C:4位

D:12位

答案:

9、单选题:

A/D转换的一般步骤包括( )、( )、( )和( )。

选项:

A:采样,保持,量化,编码

B:采样,保持,量化,译码

C:采样,量化,保持,编码

D:采样,数字化,保持,编码

答案:

10、单选题:

8位D/A转换器当输入数字量只有最高位为高电平时输出电压为5V,若只有最低位为高电平,则输出电压为( )。若输入为10001000,则输出电压为( )。

选项:

A:80mV, 2.66V

B:40mV, 5.32V

C:40mV, 2.66V

D:20mV, 5.32V

答案:

11、单选题:

将幅值上、时间上离散的阶梯电平统一归并到最邻近的指定电平的过程称为( )。

选项:

A:保持

B:采样

C:量化

D:编码

答案:

12、单选题:

10位倒T型电阻网络DAC的电阻网络中,电阻取值有( )种。

选项:

A:10

B:1

C:2

D:4

答案:

13、单选题:

8位逐次逼近型A/D转换器,如所加时钟频率为200 kHZ,则完成1次转换需要的时间为( )。

选项:

A:60µs

B:70µs

C:50µs

D:80µs

答案:

14、单选题:

下列A/D转换器速度最慢的是( )。

选项:

A:双积分型A/D转换器

B:逐次逼近型A/D转换器

C:并行比较型A/D转换器

答案:

第九章 单元测试

1、单选题:

可编程逻辑器件PLD的基本结构形式是?

选项:

A:与–或式

B:与–与式

C:或–或式

D:或–与式

答案:

2、单选题:

可以多次编程的器件是?

选项:

A:GAL

B:PLA

C:PAL

D:PROM

答案:

3、单选题:

VHDL语言程序结构中必不可少的部分是?

选项:

A:程序包

B:库

C:实体和结构体

D:配置

答案:

4、单选题:

下面哪种VHDL库使用时不需声明?

选项:

A:ASIC库

B:STD库

C:IEEE库

D:WORK库

答案:

5、单选题:

VHDL语言端口模式中不允许内部引用该端口信号的是?

选项:

A:BUFFER

B:IN

C:OUT

D:INOUT

答案:

6、单选题:

能反馈输出信号至内部的端口模式是?

选项:

A:OUT

B:BUFFER

C:IN

D:INOUT

答案:

7、单选题:

Q0为输出信号,但内部设计会用到其反馈信号,其正确的端口说明是?

选项:

A:Q0: OUT BIT

B:Q0: BUFFER BIT

C:Q0: IN BIT

D:Q0: INOUT BIT

答案:

8、单选题:

STD_LOGIC_1164程序包的正确声明方法是?

选项:

A:USE IEEE.STD_LOGIC_1164

B:USE IEEE.STD_LOGIC_1164.ALL

C:USE STD_LOGIC_1164

D:USE

答案:

9、单选题:

TYPE week IS(sun,mon,tue,wed,thr,fri,sat); week的数据类型是?

选项:

A:字符

B:枚举

C:STD_LOGIC

D:BIT

答案:

10、单选题:

VHDL语言优先级最高的运算符是?

选项:

A:OR

B:NOT

C:AND

D:XOR

答案:

11、单选题:

变量不能使用的程序结构部分是?

选项:

A:结构体

B:进程

C:过程

D:函数

答案:

12、单选题:

能在进程之间传递信息的数据对象是?

选项:

A:信号

B:变量

C:常量

D:文件

答案:

13、单选题:

signal a:bit; signal b:bit_vector(1 downto 0);下面正确的表达式是?

选项:

A:a:=b(0)

B:a<=b

C:b<=a

D:a<=b(0)

答案:

14、单选题:

a的初值为0;执行语句a<=a+1;a<=a+1; a<=a+1;后,a的值为?

选项:

A:1

B:2

C:0

D:3

答案:

15、单选题:

布尔表达式Y=AB+C的正确表达式是?

选项:

A:Y<=A AND B OR C

B:Y<= A AND (B OR C)

C:Y<=AC+C

D:Y<=A AND B +C

答案:

16、单选题:

有优先级关系的语句是?

选项:

A:条件赋值语句

B:选择赋值语句

C:简单赋值语句

D:元件例化语句

答案:

17、单选题:

在下面程序结构______中执行的语句是并行语句?

选项:

A:函数

B:过程

C:结构体

D:进程

答案:

18、单选题:

以下 语句不是顺序局。

选项:

A:if

B:loop

C:case

D:component

答案:

19、单选题:

常量的正确表达格式是?

选项:

A:CONSTANT Vcc REAL=5.0

B:CONSTANT Vcc:=5.0

C:CONSTANT Vcc:REAL=5.0

D:CONSTANT Vcc:REAL:=5.0

答案:

20、单选题:

signal a,b:bit; signal y:bit_vector(1 downto 0);下面正确的表达式是?

选项:

A:y<= b and a

B:y<=b

C:y<= b & a

D:y<=a

答案:

21、多选题:

简单的可编程逻辑器件有?

选项:

A:PAL

B:PLA

C:GAL

D:其余选项都是

E:PROM

答案:

22、多选题:

常用的顺序语句有?

选项:

A:process

B:wait

C:if

D:case

E:loop

F:block

答案:

23、多选题:

状态机描述语句一般包含以下哪几个部分?

选项:

A:主控组合进程

B:状态声明语句

C:元件例化语句

D:主控时序进程

E:辅助进程

答案:

24、多选题:

VHDL中的子程序包含以下哪些语句?

选项:

A:if语句

B:函数语句

C:元件例化语句

D:进程语句

E:过程语句

F:程序包语句

答案:

25、多选题:

VHDL中常用的库有?

选项:

A:STD

B:WORK

C:IEEE

D:ASIC

答案:

26、多选题:

VHDL语言中端口的描述有以下几种模式?

选项:

A:SIGNAL

B:IN

C:BUFFER

D:OUT

E:VARIABLE

F:INOUT

答案:

27、多选题:

一个完整的VHDL程序包含以下那几个部分?

选项:

A:程序包

B:实体

C:库

D:结构体

E:配置

答案:

28、多选题:

VHDL中有以下那几个错误等级类型用来表示系统的状态?

选项:

A:SUCCESS

B:WARNING

C:NOTE

D:OK

E:FAILURE

F:ERROR

答案:

29、多选题:

VHDL语言的数据对象有以下哪些?

选项:

A:信号

B:函数

C:常量

D:端口

E:文件

F:变量

答案:

30、多选题:

VHDL中并行信号赋值语句有以下哪几种?

选项:

A:简单信号赋值语句

B:函数调用返回语句

C:条件信号赋值语句

D:选择信号赋值语句

答案:

31、判断题:

PAL和GAL器件需要使用专门的编程器编程。

选项:

A:对

B:错

答案:

32、判断题:

断电后CPLD中的数据会丢失。

选项:

A:对

B:错

答案:

33、判断题:

INOUT是双向信号,在表达式的右边使用时信号来自外部。

选项:

A:错

B:对

答案:

34、判断题:

在VHDL中使用的库都必须声明。

选项:

A:对

B:错

答案:

35、判断题:

变量能用于VHDL内部程序间的信号传递。

选项:

A:错

B:对

答案:

36、判断题:

信号是个全局量,其赋值是立即生效的。

选项:

A:对

B:错

答案:

37、判断题:

布尔类型只能进行关系运算,不能进行算术运算。

选项:

A:对

B:错

答案:

38、判断题:

VHDL语言是一种类型特性很强的语言,要求操作对象和操作数的数据类型必须一致,不能将不同类型的信号连接起来。

选项:

A:对

B:错

答案:

39、判断题:

WAIT FOR 20ns 也能进行综合。

选项:

A:对

B:错

答案:

40、判断题:

进程语句本身是并行语句,但其内部是顺序执行的。

选项:

A:错

B:对

答案:

请先 !